## Logics gate & Boolean Algebra

#### Lecture:

- Logic gates and Boolean Algebra

- Common logical gates

- OR, AND, XOR, ...

- Logic level

- Implementation

- TTL

- CMOS based

#### Lab:

Logic gates

## Logic gate

- A gate is a circuit that operates on binary logics

- Can perform operation such as  $A = \overline{A} = A + B = A \bullet B = A \oplus B$

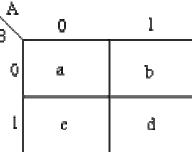

- "Truth tables" are used to present the maping of input signal into ouput signal

- Karnaugh map are used to optimize a system (we will not use this)

| A | В | F |

|---|---|---|

| 0 | 0 | 2 |

| 0 | L | Ъ |

| 1 | 0 | ¢ |

| 1 | l | d |

|   |   |   |

Truth Table.

F.

## Boolean Algebra

- Close to "classical" algebra

- Boolean Algebra allows:

- Mathematical expression of logical function,

- Manipulate variable to optimize an algorithm.

- Boolean "space"

- 2 possible value: 0 or 1

- 3 operations:

- Addition (OR + )

- Multiplication (AND × or •)

- Inversion (/ or <sup>-</sup>)

- Equations are typically sum of product or product of sum.

## Boolean Algebra (CNT'D)

#### Boole's Theorems

- $x \cdot 0 = 0$

- $x \cdot 1 = X x$

- $\bullet \quad X \cdot X = X$

- $x \cdot /x = 0$

- x + 0 = x

- x + 1 = 1

- $\bullet \quad \mathbf{X} + \mathbf{X} = \mathbf{X}$

- x + /x = 1

#### Associativity

- x + (y + z) = (x + y) + z = x + y + z

- x. (y.z) = (x.y).z = x.y.z

#### Comutativity

- $\bullet \quad \mathbf{X} + \mathbf{y} = \mathbf{y} + \mathbf{x}$

- $x \cdot y = y \cdot x$

#### Distributivity

- x.(y + z) = x.y + x.z

- (w + x).(y + z) = w.y + w.z + x.y + x.z

#### Other

- x + x.y = x

- x + /x.y = x + y

## Boolean Algebra

Morgan's theorems

$$(x + y) = x \cdot y$$

$$(x \cdot y) = x \cdot y$$

$$(x \cdot y) = x + y$$

Boolean Algebra allows to implement from a given set of logical gate any type of logical (=Boolean) equation

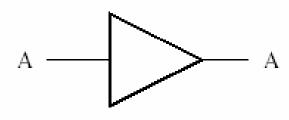

## Identity and inverter gate

#### Identity (unitary gate)

| $A_{in}$ | $A_{out}$ |

|----------|-----------|

| 0        | 0         |

| 1        | 1         |

|          |           |

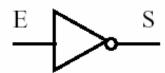

#### Inverser (N) gate

$$S = \overline{E}$$

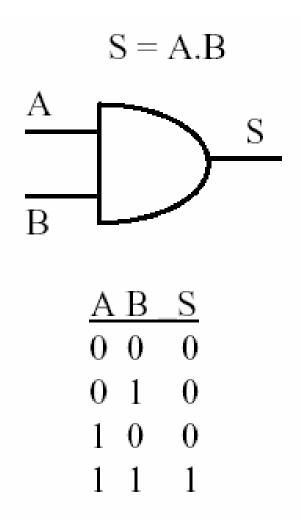

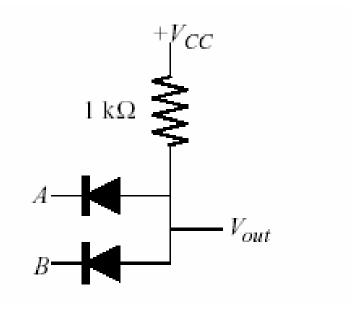

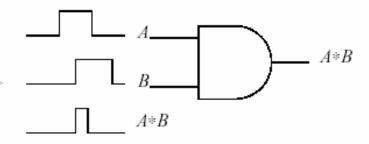

## **AND** gate

For  $V_{out}$  to be at  $+V_{CC}$  both A and B must be within 0.6 V of  $+V_{CC}$ .

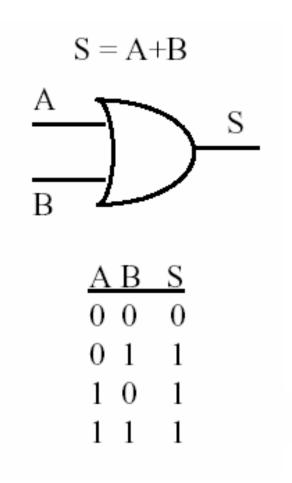

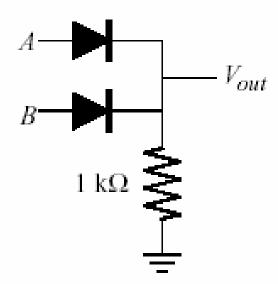

## **OR** gate

For  $V_{out}$  to not be 0 V either A or B must be over 0.6 V.

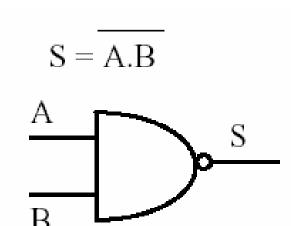

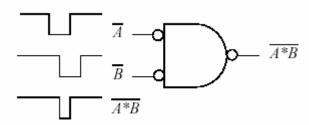

## NAND and NOR gates

| Α | В | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

$$S = \overline{A + B}$$

$$A \qquad S$$

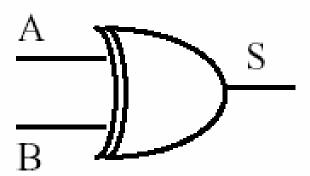

## XOR gate

$$S = A.B + A.B$$

$S = A \oplus B$

## Logic Level

- -Boolean logic

- True (T) or False (F)

- 1 ( $\equiv$  True) or 0 ( $\equiv$  True)

- Electronics level

- -High (H) Low (L)

- $-1 (\equiv High) \text{ or } 0 (\equiv True)$

- -Positive logic convention:

- -High = TRUE

-Negative logic convention:

$$-High = FLASE$$

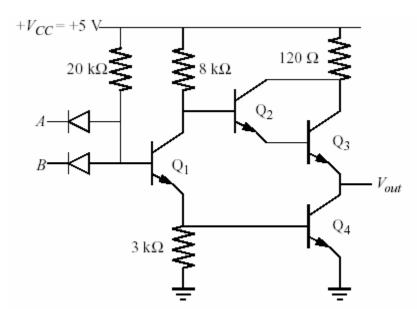

## Transistor-Transistor Logic (TTL) example of NAND function

- The diodes and 20  $k\Omega$  resistor make a simple AND-gate.

- The transistor at Q1 forms an inverter to the base of Q2 and Q4.

- The transistors Q2, Q3, and Q4 form a push-pull amplifier.

- If A and B are HIGH, the base of Q1 is at 5 V, and Q1 is on. That puts the bases of Q2 and Q4 at about 1.4 V (5V\*3Ω/11Ω) turning both on. Vout is then pulled to ground plus a C-E drop of 0.1 to 0.2 V.

- If A or B is LOW, the base of Q1 is at 0.6 V and is off. This holds the base of Q2 at 5 V and Q4 at ground. Q3 is on and Vout is at 4.4 V. due to a diode drop across the Darlington Q2Q3.

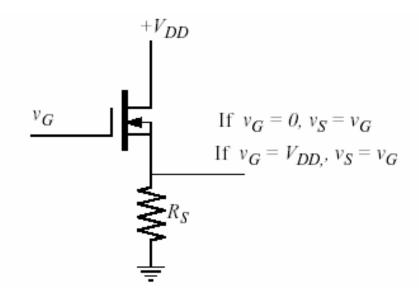

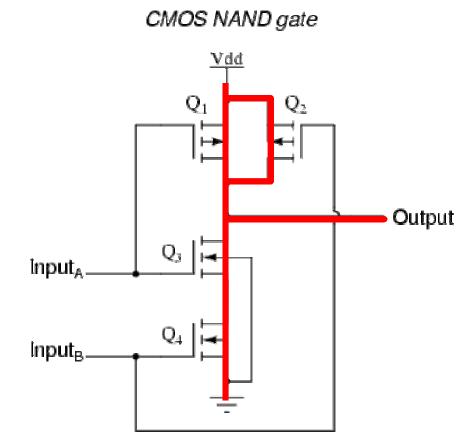

# Complementary Meta Oxide Semiconductor (CMOS)-based NAND

- The CMOS MOSFETs are connected as switches.

- A and B HIGH turn on Q3 and Q4 while turning off Q1 and Q2.

- A and B LOW turn on Q1 and Q2 while turning off Q3 and Q4.

- If both Q3 and Q4 are on then *Vout* is at ground, otherwise either Q1 or Q2 will be on pulling *Vout* up to *VDD*.

### Comparison TTL vs CMOS

- Power Supply

- TTL supply is restricted to 4.75 V to 5.25 V.

- CMOS supply can be 2 V to 6 V for HC and AC, 3 V to 15 V for 4000B, but 5 V for HCT and ACT.

- Output Signal

- TTL

- Low L if signal between 0 and 0.8 V

- High H if signal between 2 and 5 V

- CMOS

- Low L if signal is 0 V

- High is at VDD through a few hundred ohms of the MOSFET

- Speed

- TTL speeds range from 25 MHz for LS to 100 MHz for F and AS.

- CMOS speeds range from 2 MHz for 4000B to 100 MHz for AC.

## Comparison TTL vs CMOS (CNT'D)

- CMOS can be damaged by static electricity

- TTL more sensitive to noise

- CMOS consume more power (this impose some design constraint) even with low voltage operation.